JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year

JEDEC made two important announcements about the future of DRAM and non-volatile DIMMs for servers last week. Development of both is proceeding as planned and JEDEC intends to preview them in the middle of this year and publish the final specifications sometimes in 2018.

Traditionally each new successive DRAM memory standard aims for consistent jumps: doubling the bandwidth per pin, reducing power consumption by dropping Vdd/Vddq voltage, and increasing the maximum capacity of memory ICs (integrated circuits). DDR5 will follow this trend and JEDEC last week confirmed that it would double the bandwidth and density over DDR4, improve performance, and power efficiency.

Given that official DDR4 standard covers chips with up to 16 Gb capacity and with up to 2133-3200 MT/s data rate per pin, doubling that means 32 Gb ICs with up to 4266-6400 MT/s data rate per pin. If DDR5 sustains 64-bit interface for memory modules, we will see single-sided 32 GB DDR5-6400 DIMMs with 51.2 GB/s bandwidth in the DDR5 era. Speaking of modules, it is interesting to note that among other things DDR5 promises "a more user-friendly interface", which probably means a new retention mechanism or increased design configurability.

Samsung's DDR4 memory modules. Image for illustrative purposes only.

Part of the DDR5 specification will be improved channel use and efficiency. Virtually all modern random access memory sub-systems are single-channel, dual-channel or multi-channel, but actual memory bandwidth of such systems does not increase linearly with the increase of the number of channels (i.e., channel utilization decreases). Part of the problem is the fact that host cores fight for DRAM bandwidth, and memory scheduling is a challenge for CPU and SoC developers. Right now we do not know how DRAM developers at JEDEC plan to address the memory channel efficiency problem on the specification level, but if they manage to even partly solve the problem, that will be a good news. Host cores will continue to fight for bandwidth and memory scheduling will remain important, but if channel utilization increases it could mean both performance and power advantages. Keep in mind that additional memory channels mean additional DRAM ICs and a significant increase in power consumption, which is important for mobile DRAM subsystems, but it is also very important for servers.

JEDEC plans to disclose more information about the DDR5 specification at its Server Forum event in Santa Clara on June 19, 2017, and then publish the spec in 2018. It is noteworthy that JEDEC published the DDR4 specification in September 2012, whereas large DRAM makers released samples of their DDR4 chips/modules a little before that. Eventually, Intel launched the world's first DDR4-supporting platforms in 2014, two years after the standard was finalized. If DDR5 follows the same path, we will see systems using the new type of DRAM in 2020 or 2021.

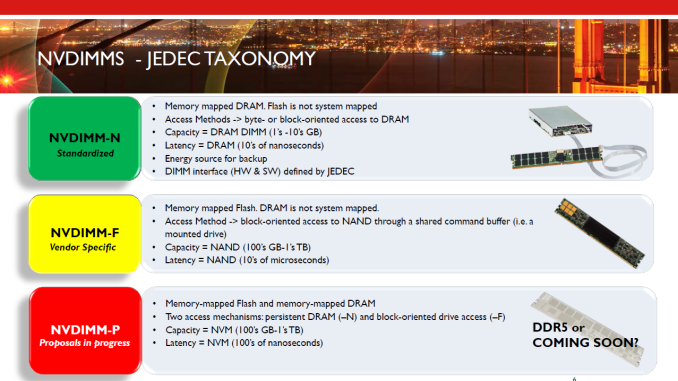

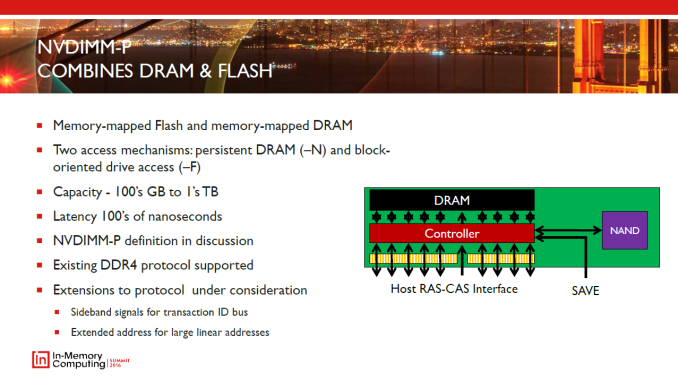

Another specification that JEDEC plans to finalize in 2018 is the NVDIMM-P that will enable high-capacity memory modules featuring persistent memory (flash, 3D XPoint, new types of storage-class memory, etc.) and DRAM. The capacity of today's NVDIMM-Ns is limited to the capacity of regular server DRAM modules, but the NVDIMM-P promises to change that and increase capacities of modules to hundreds of GBs or even to TBs. The NVDIMM-P is currently a work in progress and we are going to learn more about the tech in June.

Related Reading