Intel promises big boost to integrated GPU, breaks teraflop barrier

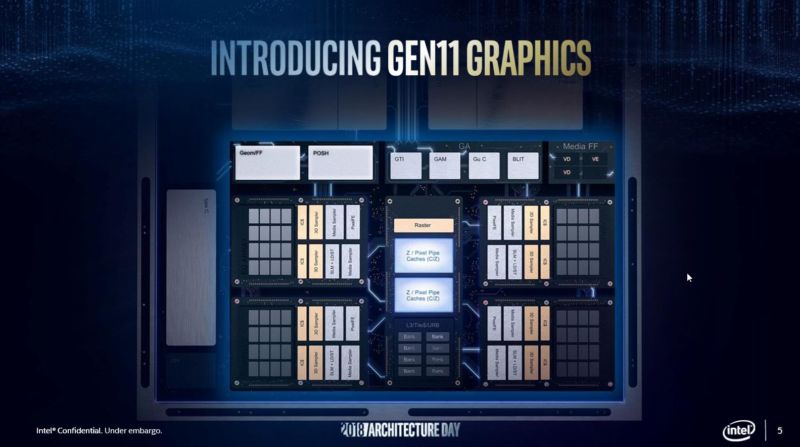

Enlarge / 64 little grey boxes means 64 execution units, up from 24. (credit: Intel)

Intel is promising a huge improvement to the performance of its integrated GPUs. Its generation 11 ("Gen11") GPU will more than double the execution units from (usually) 24 to 64, and in so doing boost the number-crunching performance to more than 1 trillion floating point operations per second.

Just as the current Gen9 GPUs, Gen11 is arranged into blocks combining execution units (EUs) with dedicated 3D hardware such as texture samplers. Gen9 parts have up to 8 EUs per block, and the most-common configuration found in Intel's processors, GT2, has three such blocks for a total of 24 EUs (though there are designs with six or nine blocks, for 48 or 72 EUs). Gen11 has 16 EUs per block and will have configurations with four blocks. It's all these extra execution units that enable that headlining 1TFLOPS performance figure.

The new GPU will use a tile-based rendering approach, which divides the image into tiles that are all rendered separately. This tends to reduce the amount of memory bandwidth the GPU needs, which is valuable in integrated GPUs, as they lack the high-performance memory found in discrete parts. The Mali GPUs designed by ARM, along with Qualcomm's Adreno GPUs, both use tile-based rendering, too.

Read 4 remaining paragraphs | Comments