Traditional semiconductor CMOS scaling at end of roadmap in 2024 then it is neuromorphic, quantum and other new systems

by noreply@blogger.com (brian wang) from NextBigFuture.com on (#2GWFD)

Traditional semiconductor scaling is expected to reach an end by about 2024, according to a white paper from engineers working on a new version of the semiconductor roadmap. The good news is a wide variety of new kinds of devices, chip stacks and systems innovations promise to continue benefits in computing performance, power and cost.

"Die cost reduction has been enabled so far by concurrent scaling of poly pitch, metal pitch, and cell height scaling. This [will likely] continue until 2024," according to one of nine white papers published today as part of the International Roadmap for Devices and Systems.

Beyond that date "there is no room for contact placement as well as worsening performance as a result of contacted poly pitch (CPP) scaling. It is projected that physical channel length would saturate around 12nm due to worsening electrostatics while CPP would saturate at 24nm to reserve sufficient CD (~11nm) for the device contact providing acceptable parasitics," the white paper reported.

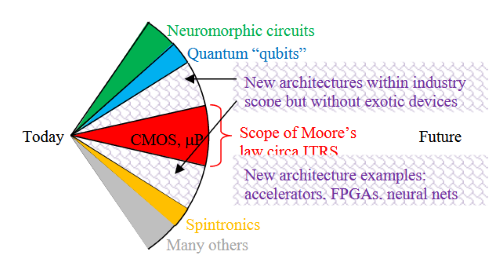

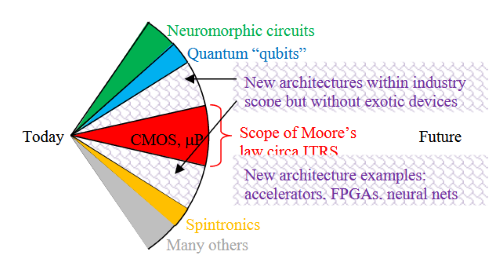

A preliminary version of a paper on new system architectures notes "many organizations are proposing remedies [to the end of Moore's law] based on new device physics. Representative new devices include neuromorphic circuits, quantum qubits, spintronics, and many others. These new devices represent a significant broadening of the search space over the previous focus on CMOS and the microprocessor"[showing a wide] deviation from the current path."

To enable such new architectures, the roadmap also includes a new section on applications benchmarks. It identifies 11 areas for tracking, spanning a broad range of computing styles.

A new section on system interconnects lays out broad challenges for both wired and wireless links. They include "increased use of germanium and III-V [materials] and possibly integration of these on silicon CMOS platforms" for advanced RF circuits.

The analysis of the future of semiconductors is here.

A preliminary paper that starts to scope out what comes after is here

Read more

"Die cost reduction has been enabled so far by concurrent scaling of poly pitch, metal pitch, and cell height scaling. This [will likely] continue until 2024," according to one of nine white papers published today as part of the International Roadmap for Devices and Systems.

Beyond that date "there is no room for contact placement as well as worsening performance as a result of contacted poly pitch (CPP) scaling. It is projected that physical channel length would saturate around 12nm due to worsening electrostatics while CPP would saturate at 24nm to reserve sufficient CD (~11nm) for the device contact providing acceptable parasitics," the white paper reported.

A preliminary version of a paper on new system architectures notes "many organizations are proposing remedies [to the end of Moore's law] based on new device physics. Representative new devices include neuromorphic circuits, quantum qubits, spintronics, and many others. These new devices represent a significant broadening of the search space over the previous focus on CMOS and the microprocessor"[showing a wide] deviation from the current path."

To enable such new architectures, the roadmap also includes a new section on applications benchmarks. It identifies 11 areas for tracking, spanning a broad range of computing styles.

A new section on system interconnects lays out broad challenges for both wired and wireless links. They include "increased use of germanium and III-V [materials] and possibly integration of these on silicon CMOS platforms" for advanced RF circuits.

The analysis of the future of semiconductors is here.

A preliminary paper that starts to scope out what comes after is here

Read more