Intel provides more details on its Arc GPUs, which will be made by TSMC

Enlarge / Intel disclosed a few more details about the Xe-HPG architecture underpinning its upcoming Arc GPUs. (credit: Intel)

Earlier this week, Intel announced Arc, the branding for the new gaming GPUs that will face off with Nvidia's GeForce and AMD's Radeon cards when they launch early in 2022. Today, Intel provided a few additional details on Arc, its underlying Xe-HPG architecture, its graphics drivers, and the "XeSS" upscaling technology that will work with both Intel's GPUs as well as GPUs from Nvidia and AMD.

The HPG in Xe-HPG stands for "high-performance gaming," and it builds on the Xe-LP ("low-power") graphics tech included in Intel's 11th-generation Tiger Lake laptop processors and the low-end DG1 dedicated GPU. At a high level, Xe-HPG will support all of the features in DirectX 12 Ultimate, just like Nvidia's RTX 2000- and 3000-series GPUs and AMD's RDNA2-based Radeon RX 6000-series cards. This includes, most notably, support for hardware-accelerated ray tracing, variable rate shading, and mesh shaders.

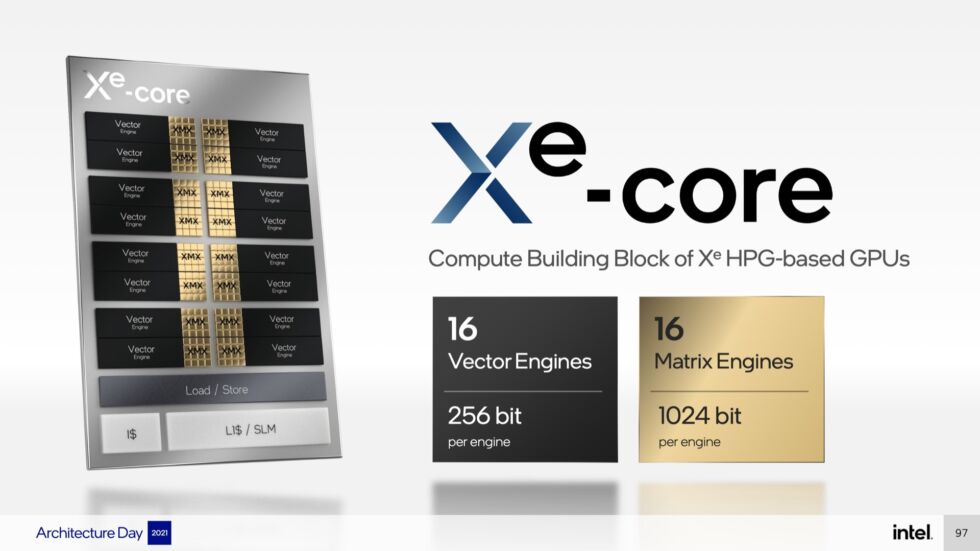

Intel is replacing the "EU" as its base GPU hardware measurement with the "Xe-core," a mix of 16 vector engines, 16 matrix engines, some cache, and a few other elements. [credit: Intel ]

Since at least 2006, Intel has talked about its GPU hardware in terms of "execution units," or EUs. The company is doing away with that terminology for Xe-HPG, replacing it instead with the concept of the "Xe-core." Each Xe-core is composed of 16 vector engines and 16 matrix (or XMX) engines, as well as L1 cache and some other hardware. Four Xe-cores combine with ray-tracing units and other fixed-function hardware to form a "render slice," which is the bare minimum any Xe-HPG GPU will need to function (along with L2 cache and a memory interface).

Read 6 remaining paragraphs | Comments