Apple introduces new M3 chip lineup, starting with the M3, M3 Pro, and M3 Max

Enlarge / Apple is introducing three M3 performance tiers at the same time. (credit: Apple)

NEW YORK-None of the new Macs that Apple is announcing at its "Scary Fast" product event today look very different from the ones they're replacing on the outside, but the inside is another story. This is the first batch of Macs to include Apple's next-generation M3-series chips, and unlike past years, Apple is introducing multiple M3 performance tiers all at the same time.

The M3, M3 Pro, and M3 Max all share the same underlying CPU and GPU architectures, the same ones used in the iPhone 15 Pro's A17 Pro chip. Also like the A17 Pro, all M3 chips are manufactured using a new 3 nm process from Taiwan Semiconductor (TSMC). Let's dive into everything we know about the M3 family's capabilities, plus the differences between each performance tier.

Meet the Apple M3 family

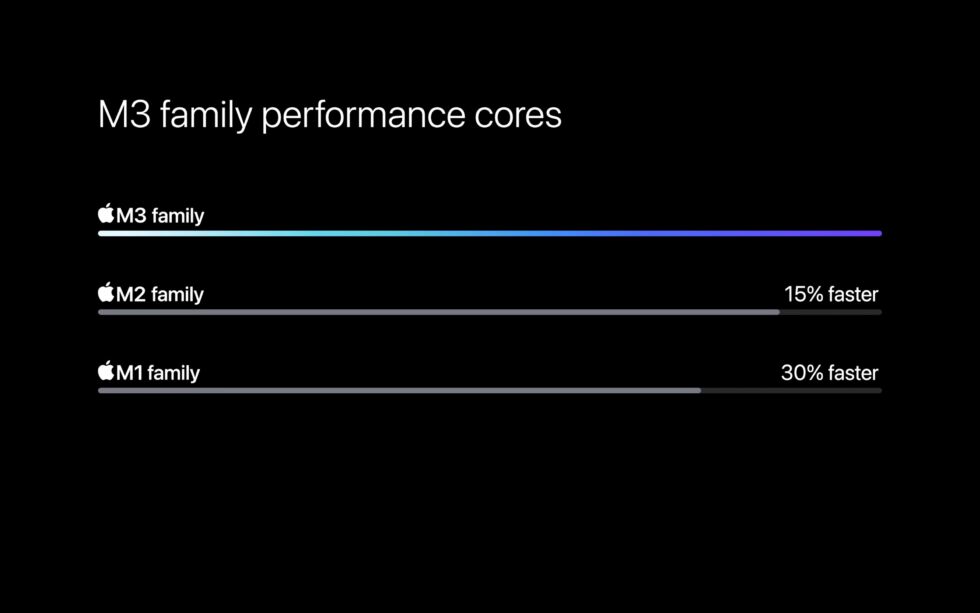

Apple prioritized comparisons to the M1 generation, which is more likely to be relevant for upgraders. But in context with the M2 numbers, M3 looks like a typical year-over-year upgrade. [credit: Apple ]

Apple says that the performance cores in any given M3 processor can run up to 30 percent faster than the M1's performance cores, and that the efficiency cores are up to 50 percent faster.Most of Apple's direct performance comparisons were to the M1 generation, which is useful insofar as M2 Mac owners aren't likely to want to spring for M3, but it has the added marketing benefit of making the performance increases sound larger than they are.