It's been a long-brewing argument, and for ages everyone has claimed that ARM chips are more power efficient due to fundamental differences in the architecture of its instruction set.

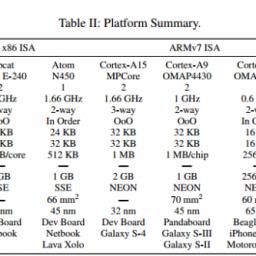

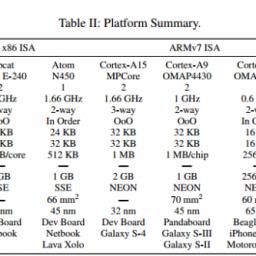

A new research paper examines these claims using a variety of ARM cores as well as a Loongson MIPS microprocessor, Intel's Atom and Sandy Bridge microarchitectures, and AMD's Bobcat.

This paper is an updated version of one I've referenced in previous stories, but its methods and claims are worth investigating in more detail. ISA investigations are intrinsically difficult given that it's effectively impossible to separate the theoretical efficiency of an architecture from the proficiency of its design team or the technical expertise of its manufacturer. Even products that seem identical can have important differences.

Extremetech looks into it via a series of benchmarks and concludes "

The RISC vs. CISC argument should've passed into history a long time ago. It may still have some relevance in the microcontroller realm, but has nothing useful to contribute to the modern era. An x86 chip can be more power efficient than an ARM processor, or vice versa, but it'll be the result of other factors - not whether it's x86 or ARM."

It's been a long-brewing argument, and for ages everyone has claimed that ARM chips are more power efficient due to fundamental differences in the architecture of its instruction set.

It's been a long-brewing argument, and for ages everyone has claimed that ARM chips are more power efficient due to fundamental differences in the architecture of its instruction set.